Klopný obvod JK: Porovnání verzí

Bez shrnutí editace |

Bez shrnutí editace |

||

| (Není zobrazeno 9 mezilehlých verzí od 2 dalších uživatelů.) | |||

| Řádek 1: | Řádek 1: | ||

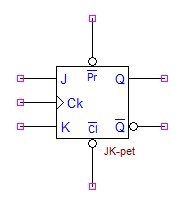

'''Schématická značka:''' [[Soubor: | '''Schématická značka:''' [[Soubor:JK-Flip-Flop.jpg]] | ||

-JK má vstupy funkčně shodné s obvodem RS: J nastavuje hodnotu logická 1, K nastavuje hodnotu logická 0. Pokud jsou oba vstupy J a K aktivní (u KO RS mluvíme o zakázaném stavu), vnitřní hodnota se při hodinovém pulzu neguje. Oproti RS se tento klopný obvod vyrábí pouze v synchronní variantě. | -JK má vstupy funkčně shodné s obvodem RS: J nastavuje hodnotu logická 1, K nastavuje hodnotu logická 0. Pokud jsou oba vstupy J a K aktivní (u KO RS mluvíme o zakázaném stavu), vnitřní hodnota se při hodinovém pulzu neguje. Oproti RS se tento klopný obvod vyrábí pouze v synchronní variantě. | ||

| Řádek 6: | Řádek 6: | ||

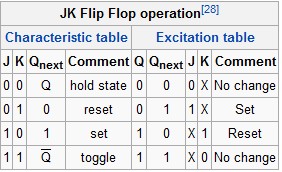

'''Pravdivostní tabulka se tak oproti KO RS liší v reakci na zakázaný stav:''' | '''Pravdivostní tabulka se tak oproti KO RS liší v reakci na zakázaný stav:''' | ||

K | {| class="wikitable" | ||

0 | ! K || J || Q<sub>n+1</sub> | ||

0 | |- | ||

1 | | 0 || 0 || Q<sub>n</sub> | ||

1 | |- | ||

| 0 || 1 || 1 | |||

|- | |||

| 1 || 0 || 0 | |||

|- | |||

| 1 || 1 || <span style="text-decoration:overline">Q</span><sub>n</sub> | |||

|} | |||

[[Soubor:JK-Flip-Flop_01.jpg|link=http://en.wikipedia.org/wiki/Flip-flop_(electronics)#JK_flip-flop]] | |||

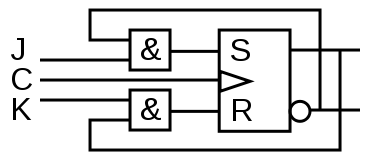

'''Schema hradla JK vyrobeného z hradla RS a ANDů:''' [[Soubor:JK-1.png]] | '''Schema hradla JK vyrobeného z hradla RS a ANDů:''' [[Soubor:JK-1.png]] | ||

http://en.wikipedia.org/wiki/Flip-flop_(electronics)#JK_flip-flop | |||

{{#widget:YouTube|id=5hJ8_UBSz6M}} | |||

{{#widget:YouTube|id=bN02shtPWuI}} | |||

Aktuální verze z 25. 2. 2014, 10:37

-JK má vstupy funkčně shodné s obvodem RS: J nastavuje hodnotu logická 1, K nastavuje hodnotu logická 0. Pokud jsou oba vstupy J a K aktivní (u KO RS mluvíme o zakázaném stavu), vnitřní hodnota se při hodinovém pulzu neguje. Oproti RS se tento klopný obvod vyrábí pouze v synchronní variantě.

-Tento obvod nese označení po vědci jménem Jack Kilby, který jej v roce 1958 představil ve firmě Texas Instruments (patent na jeho jméno vyšel o rok později). Protože název obvodu nenese žádný smysl, existuje v angličtině mnemotechnická pomůcka pro označení vstupů „jump-kill“, tedy „nahoď-zruš“.

Pravdivostní tabulka se tak oproti KO RS liší v reakci na zakázaný stav:

| K | J | Qn+1 |

|---|---|---|

| 0 | 0 | Qn |

| 0 | 1 | 1 |

| 1 | 0 | 0 |

| 1 | 1 | Qn |

Schema hradla JK vyrobeného z hradla RS a ANDů:

http://en.wikipedia.org/wiki/Flip-flop_(electronics)#JK_flip-flop