AplTVY2: Porovnání verzí

Skočit na navigaci

Skočit na vyhledávání

Bez shrnutí editace |

Bez shrnutí editace |

||

| (Není zobrazeno 5 mezilehlých verzí od stejného uživatele.) | |||

| Řádek 1: | Řádek 1: | ||

{| class="toccolours" cellpadding="5" style="float: right; clear: right; margin: 0 0 1em 1em; font-size: 85%; width: 35em" | |||

| colspan="2" style="text-align: center; font-size: larger; background-color: lightgreen;" | '''''TP od roku 2017''''' | |||

|- | |||

| | |||

T1 - BOZP – řády odborných učeben | |||

T2 - Návrh kombinačního log. obvodu | |||

T3 - Minimalizace logické funkce | |||

T4 - Simulace funkce logického obvodu na PC | |||

T5 - Realizace typického kombinačního logického obvodu | |||

T6 - Zadání úloh s multiplexorem, DeMX a sčítačkou | |||

T7 - Realizace zapojení na stavebnici | |||

T8 - Realizace sekvenčního logického obvodu SLO1 | |||

T9 - Realizace sekvenčního logického obvodu – čítač SLO2 | |||

T10 - Popis vývoje uP aplikace | |||

T11 - V/V brány, jejich vlastnosti a využití – tvorba programu pro výstupní moduly | |||

T12 - Vývoj mikroprocesorové aplikace – blikající LED | |||

T13 - Vstupní moduly – tvorba programu pro vstupní moduly | |||

T14 - Vývoj mikroprocesorové aplikace – test tlačítek | |||

T15 - T17 - Opakování | |||

|} | |||

úkoly: | úkoly: | ||

#Postavit [[Typický KLO]]: [[Multiplexor]], [[Převodník kódu]], [[Demultiplexor]], [[Dekodér]], [[Generátor parity]], [[Sčítačka]] | #Postavit [[Typický KLO]]: [[Multiplexor]], [[Převodník kódu]], [[Demultiplexor]], [[Dekodér]], [[Generátor parity]], [[Sčítačka]] | ||

| Řádek 15: | Řádek 27: | ||

===Úloha č.1=== | ===Úloha č.1=== | ||

#Realizovat | #Realizovat Sekvenční logický obvod podle předloh | ||

===Úloha č.2=== | ===Úloha č.2=== | ||

| Řádek 28: | Řádek 39: | ||

# [[Asynchronní čítač modulo 4 vpřed s D-KO]] | # [[Asynchronní čítač modulo 4 vpřed s D-KO]] | ||

# [[Synchronní čítač modulo 10 s 7490A]] | # [[Synchronní čítač modulo 10 s 7490A]] | ||

# [[Sekundová část digitálních hodin]] | # [[Sekundová část digitálních hodin s 7490A]] | ||

# [[Asynchronní čítač modulo 8 vzad s D- | # [[Asynchronní čítač modulo 8 vzad s D-KO]] | ||

# [[Synchronní čtyřbitový čítač modulo 16 s 7493A]] | # [[Synchronní čtyřbitový čítač modulo 16 s 7493A]] | ||

[[Soubor:8051-logo.gif|link=8051|8051]] [[Soubor:D10_HW_picaxe.jpg|120px|link=PICAXE|PICAXE]] [[Soubor:AVR-logo.png|120px|link=AVR|AVR]] [[Soubor:Arduino_link-01.jpg|120px|link=Arduino|Arduino]] [[Soubor:PIC-logo.jpg|100px|link=PIC|PIC]] | |||

<gallery> | |||

Soubor:D10_HW_picaxe_01.jpg|PICAXE - vývojová deska | |||

Soubor:D10_HW_picaxe_02.jpg|PICAXE - popis vývojové desky | |||

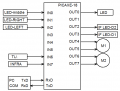

Soubor:ProfiCAD_PICAXE.png|PICAXE - blokové schéma | |||

Soubor:D10_HW_picaxe_03.jpg|PICAXE - schéma vývojové desky | |||

</gallery> | |||

<gallery> | |||

Soubor:MAT-POZADAVKY-PRA-ROBOT-UMIK.jpg|Robot Umík | |||

Soubor:Umik-popis.png|Umík - popis | |||

Soubor:Umik-blok-schema.png|Umík - blokové schéma | |||

Soubor:Robot-umík-sch.jpg|Schéma zapojení robota Umíka | |||

</gallery> | |||

<Gallery> | |||

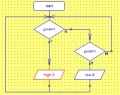

Soubor:PICAXE-vyv-diagram_01.jpg|Blik | |||

Soubor:PICAXE-vyv-diagram.jpg|2x IN, 2 x OUT | |||

</gallery> | |||

Aktuální verze z 12. 9. 2018, 07:33

| TP od roku 2017 | |

T1 - BOZP – řády odborných učeben T2 - Návrh kombinačního log. obvodu T3 - Minimalizace logické funkce T4 - Simulace funkce logického obvodu na PC T5 - Realizace typického kombinačního logického obvodu T6 - Zadání úloh s multiplexorem, DeMX a sčítačkou T7 - Realizace zapojení na stavebnici T8 - Realizace sekvenčního logického obvodu SLO1 T9 - Realizace sekvenčního logického obvodu – čítač SLO2 T10 - Popis vývoje uP aplikace T11 - V/V brány, jejich vlastnosti a využití – tvorba programu pro výstupní moduly T12 - Vývoj mikroprocesorové aplikace – blikající LED T13 - Vstupní moduly – tvorba programu pro vstupní moduly T14 - Vývoj mikroprocesorové aplikace – test tlačítek T15 - T17 - Opakování | |

úkoly:

- Postavit Typický KLO: Multiplexor, Převodník kódu, Demultiplexor, Dekodér, Generátor parity, Sčítačka

Sekvenční logické obvody

Úloha č.1

- Realizovat Sekvenční logický obvod podle předloh

Úloha č.2

Aplikace SLO

Čítače:

D-KO (7474), JK - KO (7472)

- Asynchronní čítač modulo 4 vpřed s D-KO

- Synchronní čítač modulo 10 s 7490A

- Sekundová část digitálních hodin s 7490A

- Asynchronní čítač modulo 8 vzad s D-KO

- Synchronní čtyřbitový čítač modulo 16 s 7493A

-

PICAXE - vývojová deska

-

PICAXE - popis vývojové desky

-

PICAXE - blokové schéma

-

PICAXE - schéma vývojové desky

-

Robot Umík

-

Umík - popis

-

Umík - blokové schéma

-

Schéma zapojení robota Umíka

-

Blik

-

2x IN, 2 x OUT