Syntéza SLO

Příklad návrhu:

Pro názornou ukázku jsem se rozhodl prezentovat zde mou seminární práci z předmětu CIT.

Nejdříve tedy trocha teorie

Výstup Mooreova automatu je závislý pouze na okamžitém stavu paměti, a okamžitý stav paměti je závislý na minulém stavu paměti a minulém stavu vstupu.

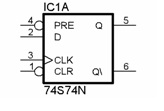

D- KO: Co přivedeme na vstup to bude také na výstupu

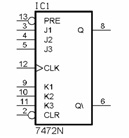

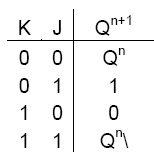

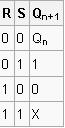

JK- KO: Obsahuje dva vstupy J a K. Přivedu- li na vstupy JK logické „0“ obvod si pamatuje, přivedu- li na J log. „1“ a na K zůstane log. „0“ výstup bude nastaven do log. „1“ (set),přivedu- li na K log. „1“ a J zůstane v log. „0“ výstup bude nastaven do log. „0“ (reset), přivedu- li na vstupy JK log. „1“ stav výstupu se změní v opačný.

Nyní přistoupím k vlastnímu zadání, mé zadání bylo složeno ze tří D klopných obvodů.

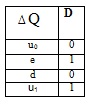

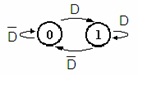

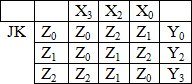

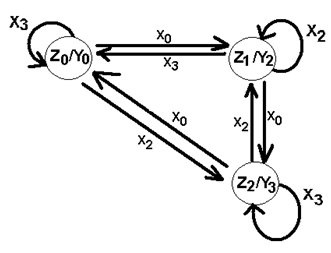

V zadání dostaneme slovní zadání, tabulku přechodů a výstupů a graf přechodů popisující chování SLO.

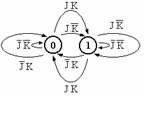

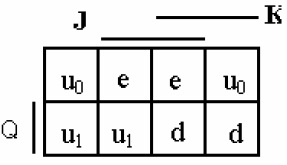

Tabulka přechodů a výstupů:  graf přechodů:

graf přechodů:

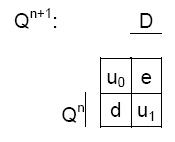

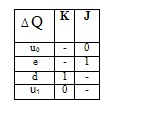

Tabulku přechodů a výstupů je třeba přetransformovat dle použitých klopných obvodů:

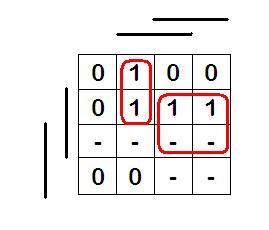

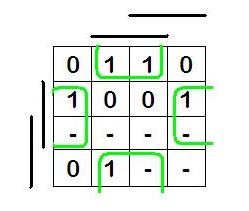

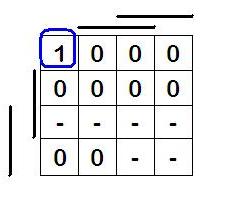

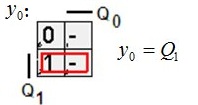

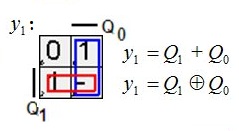

Dále provedeme minimalizaci pomocí metody Karnaughovy mapy:

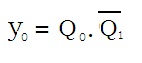

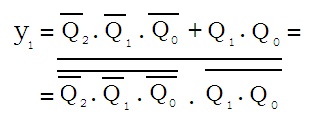

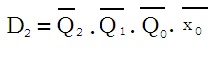

Z Karnoughových map vytvoříme výrazy:

Stejně postupujeme i s výstupy:

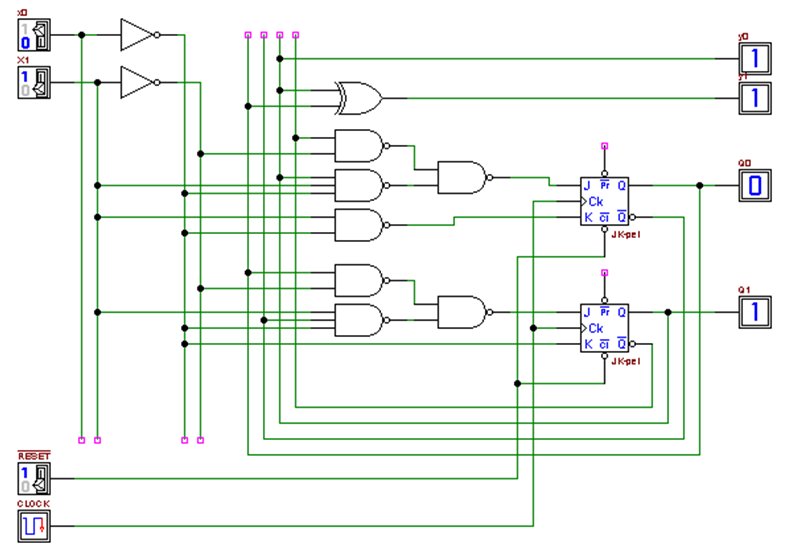

Nyní už pouze zakreslíme logickou síť:

--Rmazor 15. 4. 2010, 20:39 (UTC)