Správa pamětí grafických karet, pipelines

Paměť grafické karty

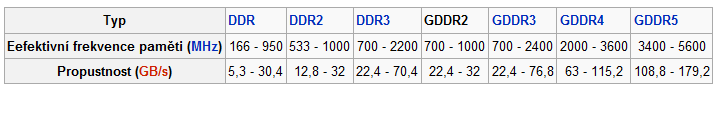

Jso do ní ukládány informace potřebné pro grafické výpočty. Integrované grafické karty využívají operační pamět celého počítače. Jinak má vlastní paměť, nejčastěji nějaký typ GDDR (GDDR 2, 3, 4, 5) nebo DDR (1, 2, 3) kvůli nižší cenně. Dříve se používali SDR. U notebooků mívají grafické karty částečně vlastní a částečně sdílenou paměť.

Pipelines

Pipelining neboli zřetězené zpracování, či překrývání strojových instrukcí. Základní myšlenkou je rozdělení zpracování jedné instrukce mezi různé části procesoru a tím i dosažení možnosti zpracovávat více instrukcí najednou. Fáze zpracování je rozdělena minimálně na 2 úseky:

1. Načtení a dekódování instrukce

2. Provedení instrukce a případné uložení výsledku

To vedlo k vytvoření procesoru složeného ze dvou spolupracujících subprocesorů (skalární architektura), kdy každá část realizuje danou fázi zpracování. Procesor má části – EU (Execution Unit) a BIU (Bus Interface Unit). Zřetězení se stále vylepšuje a u novějších procesorů se již můžeme setkat stále s více řetězci rozpracovaných informací (více pipelines). Z toho vyplývá, že je možno dokončit více, než 1 instrukci za 1 hodinový cyklus (takt procesoru).

Běžná riscová pipeline

Za jakýsi standard je považována pipeline s pěti stupni, implementována například v prvních procesorech MIPS, SPARC a Motorola 88000. Jedná se o následující stupně:

1. Instruction fetch - vyzvednutí instrukce

2. Decode - dekódování instrukce, zároveň se načítají registry

3. Execute - provedení instrukce

4. Access - čtení z paměti

5. Writeback - zápis výsledku do paměti

Predikce skoku

Jedním z problémů pipeliningu je fakt, že instrukce následující po skoku se vyzvedává dřív než je skok dokončen. Primitivní implementace vyzvedává vždy následující instrukci, což vede k tomu že se vždy mýlí, pokud je skok nepodmíněný. Pozdější implementace mají jednotku předpovídání skoku, která vždy správně předpoví (tedy předem dekóduje) nepodmíněný skok a s použitím cache se záznamem předchozího chování programu se pokusí předpovědět i cíl podmíněných skoků nebo skoků s adresou v registru nebo paměti.

V případě, že se predikce nepovede, bývá nutné vyprázdnit celou pipeline a začít vyzvedávat instrukce ze správné adresy, což znamená relativně velké zdržení.

Souvisejícím problémem je přerušení. Softwarová přerušení a výjimky jsou z hlediska procesoru skoky a je možné je predikovat, i když složitěji než obyčejné skoky. Hardwarová přerušení mohou oproti tomu dorazit kdykoliv bez předchozího upozornění, na druhou stranu v mnoha případech je možné „podvádět“ tak, že se přerušení nezačne provádět okamžitě, ale zařadí se na konec fronty, jakoby přišlo o několik instrukcí později. Znamená to ale další komplikaci při selhání predikce skoku - musí se totiž zrušit instrukce mezi skokem a přerušením, ale ne samotné přerušení, a cílovou adresu skoku uložit na zásobník pro návrat z přerušení.

Pipeline v x86

Na architektuře x86 se pipeline objevila u procesoru Intel 80286, kde měla tři stupně (Bus Unit, Instruction Unit, Execution Unit). Procesor Intel Pentium má jako první dvě pipeline (U-pipe a V-pipe a obě používají zřetězené zpracování instrukcí). Zde se poprvé objevuje pojem superskalární procesor - tzn. zřetězené zpracování instrukcí se provádí ve více než jedné frontě (konkrétně u Pentia se provádí v U-pipe i V-pipe, tzn. obě nejprve vyberou instrukci (prefetch), obě ji pak předají k dekódování (decode) atd.). Další procesory se dále komplikovaly: Intel Pentium 4 má pipeline s 31 stupni, ale je otázkou, zda toto číslo má smysl. Hlavním rozdílem totiž je, že od Pentium Pro (a AMD K5) fungují procesory x86 na principu překladu CISCových instrukcí na RISCové. První fáze tedy spočívají ve vyzvednutí instrukcí z paměti a jejich překladu na RISCové, které se pak provádějí mimo pořadí a paralelně. Může se stát i to, že jedna CISCová instrukce se rozdělí na dvě RISCové, z nichž jedna je již dokončena, zatímco druhá čeká na výkonnou jednotku.

I nejmodernější 64bitové procesory navazují na x86, ovšem zaručují, že z pohledu programátora se instrukce vykonávají sekvenčně a přerušení jsou doručena tak, že všechny instrukce před přerušením jsou dokončeny a žádná instrukce po přerušení následující neovlivnila stav procesoru. Co při vylepšování procesorů padlo jsou tabulky „ceny“ (tedy času trvání) instrukcí: spočítat, jak rychle se na moderním procesoru vykoná nějaká sekvence instrukcí je velmi obtížné a závisí na příliš mnoha parametrech, které se navíc v každém modelu procesoru liší. V dnešních procesorech jsou možná i paradoxní chování typu funkce, která trvá déle pokud z ní smažete část kódu.

Pipeline u GPU

V 3D počítačové grafice, podmínka grafické pipeline nebo renderovacích pipeline se často vztahuje na současný stav metody rasterization-based rendering.

zdroje:

http://cs.wikipedia.org/wiki/Pipelining

http://cs.wikipedia.org/wiki/Grafick%C3%A1_karta

--Jsobota 18. 6. 2010, 08:30 (UTC)