Deeds

(Rozdíly mezi verzemi)

| Řádka 1: | Řádka 1: | ||

| − | + | {| class="toccolours" cellpadding="5" style="float: right; clear: right; margin: 0 0 1em 1em; font-size: 85%; width: 30em" | |

| − | + | | colspan="2" style="text-align: center; font-size: larger; background-color: lightgreen;" | '''''Mikroprocesorová technika''''' | |

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | == | + | |

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| + | |- style="vertical-align: top;" | ||

| + | | | ||

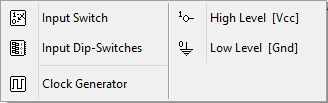

Input Components: | Input Components: | ||

| − | [[Soubor: | + | [[Soubor:Deeds_inputs.png]] |

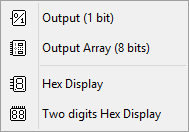

Output Components: | Output Components: | ||

| − | [[Soubor: | + | [[Soubor:Deeds_outputs.png]] |

Logic Gates: | Logic Gates: | ||

| − | [[Soubor: | + | [[Soubor:Deeds_logic_gates.jpg]] |

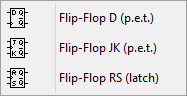

Flip Flops: | Flip Flops: | ||

| − | [[Soubor: | + | [[Soubor:Deeds_flip-flops.png]] |

| + | |||

| + | |} | ||

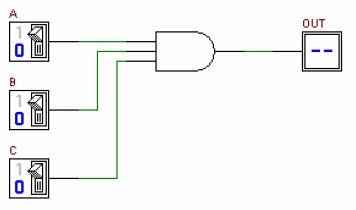

=== Test jednoduchého číslicového obvodu === | === Test jednoduchého číslicového obvodu === | ||

| − | + | [[Soubor:Deeds_O1.jpg|Deeds_O1.jpg]] | |

| + | |||

# Stáhněte a nainstalujte aplikaci | # Stáhněte a nainstalujte aplikaci | ||

# Nakreslete schéma podle zadání. | # Nakreslete schéma podle zadání. | ||

| Řádka 49: | Řádka 36: | ||

[[Soubor:Deeds_true_table.jpg|Deeds_true_table.jpg]] [[Soubor:Deeds_diagram.jpg|Deeds_diagram.jpg]] | [[Soubor:Deeds_true_table.jpg|Deeds_true_table.jpg]] [[Soubor:Deeds_diagram.jpg|Deeds_diagram.jpg]] | ||

| + | |||

| + | |||

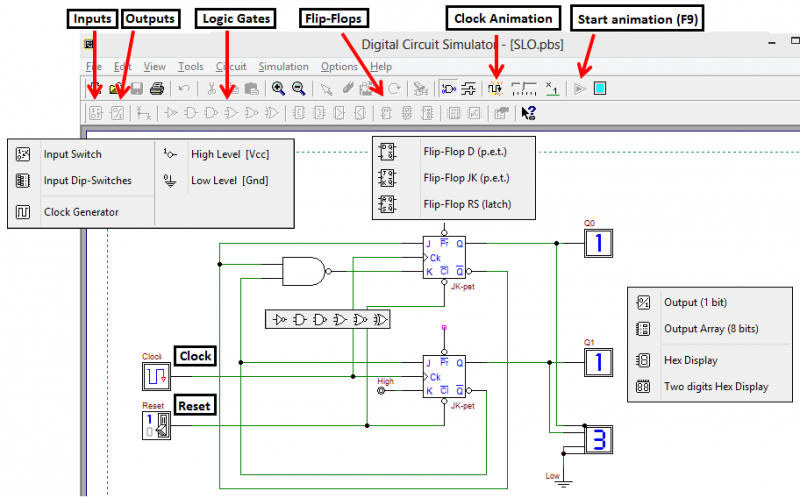

| + | == Syntéza SLO == | ||

| + | |||

| + | [[Soubor:Deeds_SLO1.png|Ukázka syntézy SLO|800px]] | ||

| + | |||

| + | |||

| + | ===Čítač M6 vpřed=== | ||

| + | |||

| + | [[Soubor:SLO_CT_M6_UP.gif|Ukázka čítače M6 vpřed]] | ||

| + | |||

| + | ===Čítač M6 vzad=== | ||

| + | |||

| + | [[Soubor:SLO_CT_M6_Down.gif|Ukázka čítače M6 vzad]] | ||

| + | |||

| + | |||

Verze z 17. 4. 2014, 08:01

| Mikroprocesorová technika | |

|

Input Components: Output Components: Logic Gates: Flip Flops: | |

Obsah |

Test jednoduchého číslicového obvodu

- Stáhněte a nainstalujte aplikaci

- Nakreslete schéma podle zadání.

- K otestování klikněte na příkaz

, který se nachází v menu.

, který se nachází v menu.

- Prozkoušejte funkčnost obvodu všemi možnými vstupními kombinacemi.

- Vyplňte pravdivostní tabulku obvodu

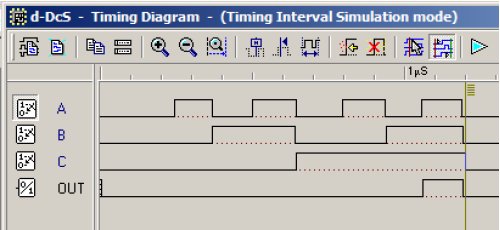

- Spusťte automatické generování časového průběhu

(Timing Diagram Simulation (F8))a porovnejte výsledky s pravdivostní tabulkou.

(Timing Diagram Simulation (F8))a porovnejte výsledky s pravdivostní tabulkou.

Pozn.: Časové průběhy vstupních proměnných se pro testování KLO musí nadefinovat.

Syntéza SLO

Čítač M6 vpřed

Čítač M6 vzad

SW:

www:

P:\SPS\PRA\SW\PC\Deeds Portable

--JA 29. 4. 2010, 09:05 (UTC)